# Wafer-Level Hysteresis-Free Resonant **Carbon Nanotube Transistors**

# Ji Cao, \*,<sup>+,+</sup> Sebastian T. Bartsch,<sup>+</sup> and Adrian M. Ionescu<sup>\*,+</sup>

<sup>†</sup>Nanoelectronics Lab, Stanford University, Stanford, California 94305, United States and <sup>‡</sup>Nanoelectronic Devices Laboratory, Ecole Polytechnique Fédérale de Lausanne (EPFL), Lausanne 1015, Switzerland

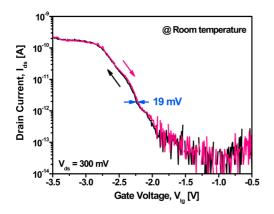

ABSTRACT We report wafer-level fabrication of resonant-body carbon nanotube (CNT) field-effect transistors (FETs) in a dual-gate configuration. An integration density of  $>10^6$  CNTFETs/cm<sup>2</sup>, an assembly yield of >80%, and nanoprecision have been simultaneously obtained. Through combined chemical and thermal treatments, hysteresis-free (in vacuum) suspendedbody CNTFETs have been demonstrated. Electrostatic actuation by lateral gate and FET-based readout of mechanical resonance have been achieved at room temperature. Both upward and downward in situ frequency tuning has been experimentally demonstrated in the dual-gate architec-

ture. The minuscule mass, high resonance frequency, and in situ tunability of the resonant CNTFETs offer promising features for applications in radio frequency signal processing and ultrasensitive sensing.

KEYWORDS: carbon nanotube · wafer-scale fabrication · nanoprecision · field-effect transistors · resonators · hysteresis-free · in situ tunina

esearch in the fields of complementary metal-oxide-semiconductor (CMOS) and a nano-electromechanical system (NEMS) is growing rapidly, aiming at future miniaturized high-performance devices. Carbon nanotubes (CNTs), in particular single-walled (SW) CNTs, stand out as a promising candidate due to their unique physical, electrical, and mechanical properties associated with high integration density and surface-to-volume ratio.<sup>1-3</sup> Suspending CNTs, compared to the ones adhered to the substrate, offer many opportunities in chemical/bio/optical/displacement sens $ing_{1}^{2-6}$  as well as in electromechanical resonance based applications such as mass sensing, radio frequency (RF) signal processing, and single-device radios.<sup>7-9</sup> The miniscule CNT mass (attogram range), high eigenfrequencies, and potentially high quality factor Q<sup>10</sup> make CNT resonators suitable for atomic scale mass/force detection.<sup>11</sup> Meanwhile, the integrated fieldeffect transistor (FET) properties strongly facilitate resonant motion detection with low power consumption.<sup>12,13</sup> Further, frequency tunability of CNT resonators is important for parametric amplification schemes or communication applications.

Currently, the actuation, resonance detection, and in situ frequency tuning of CNT resonators were typically demonstrated with a back gate.<sup>8,14,15</sup> However, the back gate configuration is not applicable for controlling and tuning individual CNT resonators in large arrays.

So far, the major challenge of manufacturing CNT-based devices has been largescale high-precision CNT integration onto CMOS circuitry. It requires that each CNT is placed at a desired location with specified direction and density in a CMOS-compatible process. Two major approaches are involved in CNT assembly: controlled CNT synthesis and CNT assembly by postsynthesis techniques. Currently, chemical assemblv<sup>16</sup> and solution-based precise assembly. e.g., resist-assisted dielectrophoresis (DEP),<sup>17</sup> are the most precise techniques for CNT CMOS devices. For NEMS applications, efforts are needed to suspend CNTs without substrate etching, which may damage the nanotubes.<sup>18</sup> Besides, in a CMOS-compatible process, nanotube devices typically get contaminated, thus lack reproducible device properties, e.g., gate hysteresis.4,19-21 Although gate hysteresis may be useful in some cases such as memory cells,<sup>22</sup>

\* Address correspondence to jicao@stanford.edu. adrian.ionescu@epfl.ch.

Received for review November 30, 2014 and accepted March 9, 2015.

Published online March 09, 2015 10.1021/nn506817v

© 2015 American Chemical Society

VOL.9 • NO.3 • 2836-2842 • 2015

2836

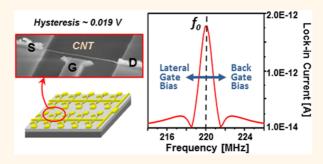

Figure 1. Wafer-scale precise assembly of CNTFETs. (a, b) View of dense CNTFET arrays with a common guiding electrode during (covered by resists) and after processing. (c-h) Resist-assisted precise DEP integration of a CNTFET simultaneous with millions of others. (i) Scanning electron microscopy (SEM) of a typical CNTFET with straightened suspended CNT body showing little slack. The lateral gate is aligned with nanoscale precision and the side view (j).

it has posed a persistent challenge in most electronic applications, resulting in inaccurate transport properties.<sup>21</sup>

To address these issues, we introduce a wafer-scale CNTFET fabrication scheme that combines the high precision of resist-assisted DEP technique<sup>12</sup> and the scalability of a capacitively coupled electrode method.<sup>23,24</sup> Individual access, high integration density, high yield, nanoprecision, and minimized contamination are the key advantages. The suspended CNTFETs exhibit negligible hysteresis in a vacuum. We electrostatically actuate individual suspended CNTFETs by lateral gates. Downward frequency tuning *via* the lateral gate and upward tuning *via* the back gate have been demonstrated. Tunable resonant CNTFETs are suitable for integration in a CMOS readout and desirable for RF signal processing and ultrasensitive sensing.

## **RESULTS AND DISCUSSION**

Wafer-Level Assembly of Suspended CNTFETs. A typical CNT lateral gate transistor fabricated by the wafer-level assembly technique as described in Materials and Methods is shown in Figure 1i, which represents the wafer-scale CNT array (Figure 1b). The suspended CNT channel is aligned to the desired position with nanoprecision, showing little slack or tension as well as negligible resist residue from the side view in Figure 1j. The lateral gate was aligned 112 nm away from the CNT body, ensuring strong gate—channel coupling for CNTFETs and electromechanical coupling for CNT resonators.

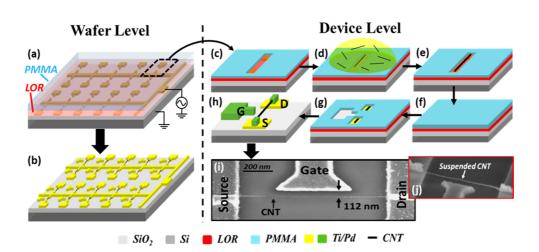

The statistical results from 10 wafers (Figure 2a) indicate that DEP duration plays a crucial role in precise CNT integration. When DEP duration is optimized (45 s in this work), on average, >80% guiding electrodes turned out to be spanned by one individual CNT or a small bundle (Figure 2b).

By the precise assembly technique, the suspendedbody CNTFETs could be further scaled: the CNT channel length and the CNT–lateral gate distance could be brought arbitrarily close within EBL resolution; the guiding electrode area could be decreased according to the limitation of the capacitively coupled electrode scheme.<sup>17,24</sup> Estimated based on these geometrical limitations, an array consisting of 400 CNT devices can be fabricated simultaneously in a 100  $\mu$ m × 100  $\mu$ m area, giving a high density of 3–4 million nanotube transistors per cm<sup>2</sup>. It is comparable to current ultra-large-scale integration (ULSI) complexity.<sup>24</sup>

The high-yield fabrication scheme featuring precisely controlled location, orientation, and shape of individual CNTs is promising for future commercialization of CNT-based devices.

**Static Electrical Characterizations.** Static measurements of the lateral-gate-suspended CNTFETs were performed in a high-vacuum probe station, Suess Microtech PMC 150. Base pressure is set below  $10^{-6}$  Torr to exclude the influence of the charge traps originating from attached water molecules.

Figure 3 shows the transfer characteristics of the suspended CNTFET shown in Figure 1i. It operates as a laterally gated p-type FET. We obtained an  $I_{on}/I_{off}$  ratio of  $\sim 10^4$  at  $V_{ds} = 0.3$  V and a subthreshold swing of SS = 220 mV/decade. The off currents ( $I_{off}$ ) are at the detection limits of the measurement system (fA level). This indicates that the device has a very low or no leakage current, which is an important feature for low power consumption. The transfer characteristics suggest that the suspended CNT channel is effectively controlled by the lateral gate though a 112 nm air gap (vacuum). The on-state resistance could be greatly improved by further annealing the CNTFETs at higher temperature (600–800 °C) in a vacuum or forming gas.<sup>25</sup>

As shown in Figure 3, negligible gate hysteresis is observed in a vacuum when the gate bias is swept

VOL. 9 • NO. 3 • 2836-2842 • 2015

AGNANC www.acsnano.org

Figure 2. (a) Histogram of yield of wafer-level precise CNT assembly technique (featuring one or one small bundle of CNT/ electrode pairs) at different DEP duration. Insets: Possible failure including missing CNTs, multiple CNTs, and misaligned CNTs. (b) Box plot of the yields of 10 wafers processed by the CNT assembly technique at 45 s DEP duration. It shows the variation of the bridging yields (>80%). The max/min, mean, and 1.5IQR (interquartile ranged) values are shown.

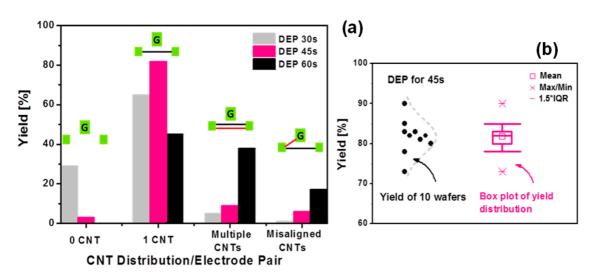

Figure 3. Transfer characteristics of the suspended CNTFET (Figure 2i) in forward and backward sweeps at room temperature. Negligible hysteresis of the device with a clean CNT body is observed in a vacuum.

forward and backward between -3.5 and -0.5 V. The hysteresis in gate voltage is as low as 0.019 V in a vacuum, and the hysteresis in current is 1 pA, which corresponds to 0.5% of  $I_{on}$  (~0.2 nA). The hysteresis of our device is comparable with one of the best records (in vacuum) reported in the CNTFETs fabricated by resist-free CNT growth.<sup>19,21</sup> Negligible hysteresis here is believed to be a key advantage of the clean suspended CNT surface. Hence, the transfer characteristics have not been disturbed by charge traps originating from the substrate, the resist residue, the surfactant, or the water molecules on the surface of the CNT channel.

In general, gate hysteresis is attributed to the charging of traps that shield the CNT from the gate, thereby shifting the threshold voltage of the device. In conventional CNTFET fabrication, the CNT gets contaminated due to direct contact with the photoresist, which is used to define the contacts. The resist residue wrapping the CNT may fully/partially isolate the CNT

channel from the gate, causing hysteresis. The complete removal of such contamination is challenging. Techniques, such as aggressive  $O_2$  plasma used for semiconductor devices, could damage the CNTs. Moreover, in suspended CNTFET fabrication, the water molecules and the surfactant induced by the aqueous solution may get wrapped around the CNT channel by the resist residue and become the sources of charge traps. The contamination cannot be eliminated by simple annealing. In other words, the complex contamination consisting of resist residue, water molecules, and surfactant can influence the density of charge traps and hence the hysteresis.

Therefore, it is crucial to develop an efficient way to remove contamination without damaging the CNT channels.<sup>26</sup>

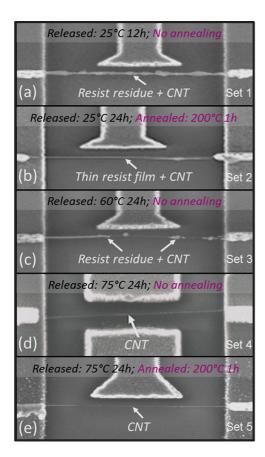

To investigate the effect of chemical and thermal treatments on gate hysteresis, we compared five sets of CNTFETs with various release and annealing conditions: resist removal temperature, release duration, and annealing conditions. Microposit Remover 1165 was used to dissolve the resists and release the devices. Annealing was performed under vacuum.

As shown in Figure 4a, all CNT channels in set 1 (released at 25 °C for 12 h; no annealing) are covered by a large amount of resist. In set 2 (released at 25 °C for 24 h; annealed at 200 °C for 1 h) (Figure 4b), typically, only a thin film of resist is left on the CNT surface.<sup>27,28</sup> The amount of resist in set 3 (released at 60 °C for 24 h; no annealing) is further reduced, leaving part of the CNT surface exposed without obvious resist coating (Figure 4c). In set 4<sup>29</sup> (released at 75 °C for 24 h; no annealing) and set 5 (released at 75 °C for 24 h; annealed at 200 °C for 1 h), the CNT channels of all samples appear to be very clean with hardly any resist residue (Figure 4d and e).

VOL.9 • NO.3 • 2836-2842 • 2015 A

Figure 4. Typical SEM images of the suspended CNTFETs with different release (with Microposit Remover 1165) and annealing (in a vacuum) conditions: (a) released at room temperature for 12 h, no annealing; (b) released at room temperature for 24 h, annealed at 200 °C for 1 h; (c) released at 60 °C for 24 h, no annealing; (d) released at 75 °C for 24 h, no annealing; (e) released at 75 °C for 24 h, annealed at 200 °C for 1 h. Obvious resist amount change can be observed.

The above experimental results imply that higher removal temperature and longer release duration give rise to the release efficiency.

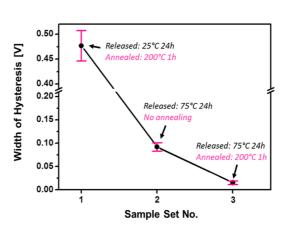

We measured hysteresis characteristics of three sets (sets 2, 4, and 5) of CNTFETs at room temperature (RT) in a vacuum.

From the statistical data in Figure 5, one can see that the voltage width of the hysteresis gets smaller as the resist residue on the CNT surface diminishes. Two heavily contaminated CNTFETs as in set 2 (Figure 4b) show a relatively large hysteresis width, ~0.45 V. Hysteresis of the clean suspended CNTFET in set 4 (Figure 4d) decreases to ~0.09 V. Note that the gate hysteresis of the annealed CNTFET in set 5 (Figure 4e) has been significantly reduced to ~0.019 V (Figure 5). The dramatic decrease in gate hysteresis proves that (1) a higher release temperature helps to dissolve the resist, thus less contamination is left on the CNT surface to provide charge traps, and (2) the annealing step effectively eliminates the water molecules and absorbates on the exposed CNT channel; hence the hysteresis is suppressed.

**CNT Resonator Characterizations.** Suspended CNTFETs with good performance serve as a solid basis for

Figure 5. Statistical data of the gate hysteresis of the suspended CNTFETs measured under vacuum (as shown in Figure 4b, d, and e) with different chemical/thermal treatments. Hysteresis reduction with optimized treatments in this work indicates minimized contamination on the CNT surface, ensuring high accuracy and resolution in sensing.

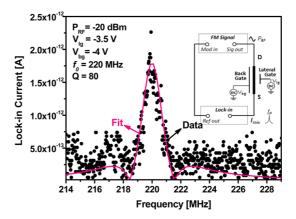

Figure 6. (a) Transmission characteristic of the resonant CNTFET (750 nm long) measured at room temperature along with a Lorentzian fit. Inset: Frequency-modulated (FM) mixing measurement setup.

detecting the mechanical resonance of the CNTs using FET-based readout. The mixing current for the resonant CNTFET at RT is shown in Figure 6 with  $V_{lg}$ = -3.5 V and back gate bias  $V_{bg}$ = -4 V. A good Lorentzian fit to the experimental data was obtained. The resonance frequency  $f_0$  was extracted to be ~220 MHz, and a quality factor Q of ~80 was obtained. A very low background noise floor (<5 × 10<sup>-13</sup>A) has been observed as expected in our low-leakage CNTFETs by the frequency-modulated (FM) technique,<sup>30</sup> which made it possible to detect the ultralow mixing current (2.3 × 10<sup>-12</sup>A).

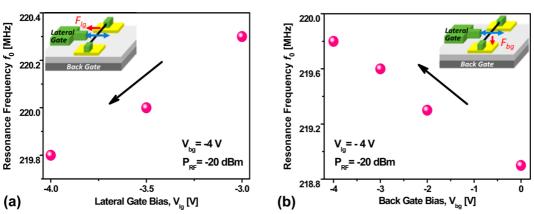

Generally, gate-induced frequency tuning of NEM resonators is attributed to two mechanisms:<sup>31</sup> (1) the capacitive softening effect, which decreases the resonance frequency due to the nonlinearity of the electrostatic force; and (2) the elastic hardening effect, which increases the resonance frequency due to the increased beam tension.

In conventional back-gated CNT resonators, CNT motions are perpendicular to the electric field direction,

VOL. 9 • NO. 3 • 2836-2842 • 2015 A

Figure 7. (a) Downward resonance frequency tuning of the resonant CNTFET by the lateral gate at room temperature. (b) Upward resonance frequency tuning of the same resonant CNTFET by the back gate at room temperature. Insets: Schematics of the resonant CNTFET in two tuning modes.

resulting in negligible capacitive softening. However, our dual-gate configuration (lateral and back gates) and narrow gate—CNT gaps offer opportunities to tune the resonant frequency *in situ* with more freedom.

The ac signal applied to the drain terminal introduces flexural motion inside the lateral electrode plane (the "in-plane" mode). When  $V_{lg}$  is applied, the electrostatic force  $F_{lg}$  is in the direction of the CNT motion. Therefore, both tension and a capacitive softening effect are created. Figure 7a shows that the resonant frequency  $f_0$  shifts downward as  $V_{lg}$ increases. A frequency tuning of ~0.2% by a  $V_{lg}$ variation of 1 V was obtained. The net effect of  $F_{lg}$ appears to be softening the effective spring constant, which reduces  $f_0$ .

On the other hand, when  $V_{bg}$  is applied to the back gate, the electrostatic force  $F_{bg}$  is perpendicular to the CNT motion and only induces tension by pulling the CNT toward the back gate. Therefore, an increase of  $V_{bg}$ provides elastic hardening, which gives rise to  $f_0$ (Figure 7b). The resonance frequency can be tuned  $\sim 0.1\%$  by a  $V_{bg}$  variation of 1 V. Here, low  $V_{lg}$  and  $V_{bg}$ were applied in case the CNT got destroyed.

*In situ* upward and downward tuning have been demonstrated within the same CNT resonator configuration. For both tuning modes, the tuning efficiencies are considered good for CNT resonators operating at these resonance frequencies.<sup>11,12</sup> The dual-gate configuration and upward/downward frequency tunability give more freedom for RF communication design where the center frequency of the filter can be fine-tuned. Besides, the individually addressable tunable CNT resonators in arrays can serve as sensing pixels, which make a large-scale sensor network feasible.

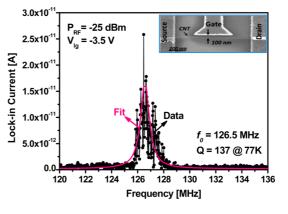

Figure 8 displays the resonance response of a resonant CNTFET with a 1  $\mu$ m channel at 77 K. The resonance frequency was extracted to be ~126.5 MHz, and the quality factor *Q* has been greatly improved to ~135. In our case, the CNT body length is on the same order of magnitude with the acoustic phonon mean

Figure 8. (a) Transmission response of a resonant CNTFET (1  $\mu$ m long) measured at 77 K along with a Lorentzian fit. Inset: SEM of the measured suspended CNTFET.

free path (0.5–1  $\mu$ m). Higher Q may be associated with lower temperature T due to the thermoelastic effect  $(Q^{-1} \sim T^2)$ .<sup>12</sup> Clamping losses, surface effects, and contamination from processing could also influence the dissipation.

Due to very low mass and atomic structure, CNTs are ideal for ultra-high-resolution sensing. With further optimization of the readout and quality factor, such resonant CNTFETs could provide a mass detection noise floor at the zg level, which is interesting for ultra-high-resolution mass sensing.<sup>32</sup>

### CONCLUSION

In conclusion, we report wafer-scale suspended CNTFET fabrication with high precision, yield, and density as well as negligible hysteresis under vacuum. Lateral gate electrostatic actuation and FET-based detection of the resonant CNTFETs have been achieved at RT. Thanks to the dual-gate configuration (lateral and back gates), the resonance frequency of the resonant CNTFETs can be tuned *in situ* either upward or downward at RT. These results provide valuable insight into the future commercialization of CNT-based

AKUCL

VOL. 9 • NO. 3 • 2836-2842 • 2015

www.acsnano.org

NEMS systems for ultrasensitive mass sensing and RF communications. The suspended-body structures also

serve as the basis for more complex digital and nondigital applications.

#### MATERIALS AND METHODS

**Wafer-Level Fabrication of Suspended CNTFETs.** The assembly of SWCNTs was performed under ambient conditions. The CNT suspension was prepared using commercially available SWCNTs (SG 65i) purchased from SWeNT Inc. (Supporting Information).

Figure 1a-h show the schematic of the electrode arrangement at wafer level (Figure 1a,b) and the detailed assembly process at the device level (Figure 1c-h).

Guiding electrode pairs and alignment markers were patterned on a SiO<sub>2</sub> (500 nm)/Si substrate (Figure 1a). In this setup, for each guiding electrode pair, one electrode was connected to a common electrode (labeled as "ce"), and the floating one (labeled as "fe") was capacitively coupled to the underlying substrate (back electrode, labeled as "be"). Between each "ce-fe" electrode pair, a 30 nm wide trench was transferred to the resist layers (100 nm LOR/50 nm PMMA) by e-beam lithography (EBL) (Figure 1a and c).

The ac signal was applied between the common electrode and the silicon substrate for 45 s (Figure 1a and d). Individual SWCNTs in solution were simultaneously attracted and aligned into each trench (Figure 1e). For high electric-field frequencies (>100 kHz), "fe" electrodes are capacitively coupled to the substrate, which allows grounding all "fe" without probing them one by one.

CNT clamps and lateral gates were precisely defined on a second PMMA layer by EBL and deposited by metal lift-off (Figure 1f.g). Resists were stripped in Microposit Remover 1165 at 75 °C for 24 h, and slack was minimized by critical point drier (Figure 1b and h). Annealing at 200 °C in a vacuum for 1 h was applied. The suspension height is adjustable by the LOR thickness.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. We would like to thank Dr. S. Xie for many useful comments. We also would like to thank the funding source: the Swiss Nanotera project CABTURES.

*Supporting Information Available:* Details of (a) CNT suspension preparation; (b) output characterization; (c) lateral gate tuning; (d) back gate tuning; (e) static characterization at 77 K. This material is available free of charge *via* the Internet at http://pubs.acs.org.

#### **REFERENCES AND NOTES**

- 1. Dresselhaus, M. S.; Dresselhaus, G.; Saito, R. Physical Properties of Carbon Nanotubes. *Carbon* **1995**, *33*, 883.

- Franklin, N. R.; Wang, Q.; Tombler, T. W.; Javey, A.; Shim, M.; Dai, H. Integration of Suspended Carbon Nanotube Arrays into Electronic Devices and Electromechanical Systems. *Appl. Phys. Lett.* **2002**, *81*, 913–915.

- Ionescu, A. M.; De Michielis, L.; Dagtekin, N.; Salvatore, G.; Cao, J.; Rusu, A.; Bartsch, S. Ultra Low Power: Emerging Devices and Their Benefits for Integrated Circuits. 2011 IEEE International Electron Devices Meeting (IEDM) 2011, 16.1.1–16.1.410.1109/IEDM.2011.6131563.

- Helbling, T.; Hierold, C.; Durrer, L.; Roman, C.; Pohle, R.; Fleischer, M. Suspended and Non-Suspended Carbon Nanotube Transistorsf NO<sub>2</sub> Sensing – A Qualitative Comparison. *Phys. Status Solidi B* **2008**, *245*, 2326–2330.

- Mann, D.; Kato, Y. K.; Kinkhabwala, A.; Pop, E.; Cao, J.; Wang, X.; Zhang, L.; Wang, Q.; Guo, J.; Dai, H. Electrically Driven Thermal Light Emission from Individual Single-Walled Carbon Nanotubes. *Nat. Nanotechnol.* 2007, *2*, 33–38.

- Stampfer, C.; Jungen, A.; Linderman, R.; Obergfell, D.; Roth, S.; Hierold, C. Nano-Electromechanical Displacement Sensing Based on Single-Walled Carbon Nanotubes. *Nano Lett.* 2006, *6*, 1449–1453.

- Jensen, K.; Kim, K.; Zettl, A. An Atomic-Resolution Nanomechanical Mass Sensor. *Nat. Nanotechnol.* 2008, 3, 533– 537.

- Sazonova, V.; Yaish, Y.; Ustünel, H.; Roundy, D.; Arias, T. A.; McEuen, P. L. A Tunable Carbon Nanotube Electromechanical Oscillator. *Nature* 2004, *431*, 284–287.

- Rutherglen, C.; Burke, P. Carbon Nanotube Radio. Nano Lett. 2007, 7, 3296–3299.

- van Beek, J.T. M.; Puers, R. A Review of MEMS Oscillators for Frequency Reference and Timing Applications. J. Micromech. Microeng. 2012, 22, 013001.

- Eichler, A.; Moser, J.; Chaste, J.; Zdrojek, M.; Wilson-Rae, I.; Bachtold, A. Nonlinear Damping in Mechanical Resonators Made from Carbon Nanotubes and Graphene. *Nat. Nanotechnol.* 2011, *6*, 339–342.

- 12. Sazonova, V. A Tunable Carbon Nanotube Resonator. Ph.D. Thesis, Cornell University, Ithaca, NY, 2006.

- 13. Ustunel, H.; Roundy, D.; Arias, T. A. Modelling A Suspended Nanotube Oscillator. *Nano Lett.* **2005**, *5*, 523–526.

- Steele, G. A.; Huttel, A. K.; Witkamp, B.; Poot, M.; Meerwaldt, H. B.; Kouwenhoven, L. P.; van der Zant, H. S. J. Strong Coupling between Single-Electron Tunneling and Nanomechanical Motion. *Science* **2009**, *325*, 1103–1107.

- Witkamp, B.; Poot, M.; van der Zant, H. S. J. Bending-Mode Vibration of a Suspended Nanotube Resonator. *Nano Lett.* 2006, 6, 2904–2908.

- Park, H.; Afzali, A.; Han, S.-J.; Tulevski, G. S.; Franklin, A. D.; Tersoff, J.; Hannon, J. B.; Haensch, W. High-Density Integration of Carbon Nanotubes via Chemical Self-Assembly. *Nat. Nanotechnol.* 2012, 7, 787–791.

- Cao, J.; Nyffeler, C.; Lister, K.; Ionescu, A. M. Resist-Assisted Assembly of Single-Walled Carbon Nanotube Devices with Nanoscale Precision. *Carbon* **2012**, *50*, 1720–1726.

- Lu, J.; Kopley, T.; Dutton, D.; Liu, J.; Qian, C.; Son, H.; Dresselhaus, M.; Kong, J. Generating Suspended Single-Walled Carbon Nanotubes across a Large Surface Area via Patterning Self-Assembled Catalyst-Containing Block Copolymer Thin Films. J. Phys. Chem. B 2006, 110, 10585– 10589.

- Nygard, J.; Cobden, D. H. Quantum Dots in Suspended Single-Wall Carbon Nanotubes. *Appl. Phys. Lett.* 2001, 79, 4216–4218.

- Cao, H.; Wang, Q.; Wang, D.; Dai, H. Suspended Carbon Nanotube Quantum Wires with Two Gates. *Small* 2005, 1, 138–141.

- Kim, W.; Javey, A.; Vermesh, O.; Wang, Q.; Li, Y.; Dai, H. Hysteresis Caused by Water Molecules in Carbon Nanotube Field-Effect Transistors. *Nano Lett.* **2003**, *3*, 193–198.

- Radosavljević, M.; Freitag, M.; Thadani, K. V.; Johnson, A. T. Nonvolatile Molecular Memory Elements Based on Ambipolar Nanotube Field Effect Transistors. *Nano Lett.* 2002, 2, 761–764.

- Krupke, R.; Hennrich, F.; Weber, H.; Kappes, M.; Löhneysen, H. Simultaneous Deposition of Metallic Bundles of Single-Walled Carbon Nanotubes Using Ac-Dielectrophoresis. *Nano Lett.* 2003, *3*, 1019–1023.

- Vijayaraghavan, A.; Blatt, S.; Weissenberger, D.; Oron-Carl, M.; Hennrich, F.; Gerthsen, D.; Hahn, H.; Krupke, R. Ultra-Large-Scale Directed Assembly of Single-Walled Carbon Nanotube Devices. *Nano Lett.* 2007, *7*, 1556–1560.

- Martel, R.; Derycke, V.; Lavoie, C.; Appenzeller, J.; Chan, K.; Tersoff, J.; Avouris, Ph. Ambipolar Electrical Transport in Semiconducting Single-Wall Carbon Nanotubes. *Phys. Rev. Lett.* 2001, *87*, 256805.

- Shimauchi, H.; Ohno, Y.; Kishimoto, S.; Mizutani, T. Suppression of Hysteresis in Carbon Nanotube Field-Effect Transistors: Effect of Contamination Induced by Device Fabrication Process. Jpn. J. Appl. Phys. 2006, 45, 5501–5503.

- 27. Cao, J.; Ionescu, A. M. Lateral Gate Suspended-Body Carbon Nanotube Field-Effect-Transistors with Sub-100nm Air Gap by Precise Positioning Method. *69th Annual Device Research Conference (DRC)* **2011**, 189– 19010.1109/DRC.2011.5994482.

- Cao, J.; Ionescu, A. M. Self-Aligned Back-Gated Suspended Body Single-Walled Carbon Nanotube Field-Effect-Transistors Fabricated by High-Precision Positioning Method. International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA) 2011, 1–210.1109/ VTSA.2011.5872223.

- Cao, J.; Ionescu, A. M. Self-Aligned Lateral Dual-Gate Suspended-Body Single-Walled Carbon Nanotube Field-Effect Transistors. *Appl. Phys. Lett.* **2012**, *100*, 063103.

- Gouttenoire, V.; Barois, T.; Perisanu, S.; Leclercq, J.-L.; Purcel, S. T.; Vincent, P.; Ayari, A. Digital and FM Demodulation of A Doubly-Clamped Single Wall Carbon Nanotube Oscillator: Towards a Nanotube Cell Phone. *Small* **2010**, *6*, 1060.

- Wu, C.; Zhong, Z. Capacitive Spring Softening in Single-Walled Carbon Nanotube Nanoelectromechanical Resonators. *Nano Lett.* 2011, 11, 1448.

- 32. Ekinci, K.; Roukes, M. Nanoelectromechanical Systems. *Rev. Sci. Instrum.* 2005, *76*, 061101.